切割发生在半导体工艺流程的末端。 此时,传统上,晶圆最终通过锯切或激光切割等方式被分为单块芯片/晶粒。 (查看我们的等离子切割101系列的第一篇文章,文章对刀片和激光等传统切割方法与等离子切割方法进行了比较)。

“与刀片或激光器相比,等离子切割作为一种可行的解决方案已经在半导体行业中得到了认可,尤其是在芯片越来越小、越来越薄、越来越复杂的情况下。”

Richard Barnett,蚀刻产品负责人

等离子切割:深入了解

等离子切割使用博世硅刻蚀工艺,这是一种在沉积和蚀刻之间交替以在晶圆中创建特征的多步骤方法。 硅和氟化物之间的化学反应是放热的,这意味着该工艺本身会产生热量。 旨在通过使用静电夹紧来管理Rapier-S工艺模块。 通过保持晶圆与冷却压板紧密接触,工艺得以持续进行,可保护晶粒和胶带,使其不会因过热而遭到任何损坏。

更加清洁的处理

等离子体切割是一种非常洁净的分离方法。 与刀片或激光切割不同,等离子切割方法不会产生任何粒子。 在切割刻蚀过程中,硅与氟发生反应并简单地汽化。 氟碳聚合物是博世工艺的关键要素,在蚀刻完成后,它会留在蚀刻特征的侧壁上。 然而,后续步骤可以完全去除这些聚合物,使等离子切割成为与刀片或激光相比最干净的方法。 这种清洁度对于晶粒与其他晶粒结合的集成(形成复杂的多晶粒封装)步骤至关重要。 成功的接合有赖于洁净的表面和清晰的晶粒边缘,以免接合面出现空隙。

每个晶圆更多晶粒

通过等离子切割,芯片制造商可以使用更窄的切口宽度(即划片线间距,也就是切割晶圆时在晶粒之间保留的空间)。 在处理RF-ID标签(通常为<0.5mm x 0.5mm)等小晶粒时尤为实用。 转而采用等离子切割技术后,宝贵的晶圆空间不再被浪费,每个晶圆可生产出更多产品。 根据晶粒尺寸的不同,这种好处可能是巨大的,并减少了对其他晶圆、工艺材料和前端设备的总体需求,以提高产量。

功能更强大的晶粒

切割后保持晶粒完整性的能力同样重要。 等离子切割是保持晶粒强度的首选方法,因为已知的替代切割方法会导致内部和表面裂纹、热影响区或碎裂等损坏。

Imec发表的一篇论文指出,采用等离子切割方法制造的晶粒强度高于所有其他参与测试的切割方法,包括激光凹槽法(无论是否配合等离子切割)以及隐切和刀切激光凹槽法。 此外,由于在晶粒周围没有发现任何空隙,因此,通过等离子切割的模具具有最佳的结合性能。 imec得出结论,对于晶粒到晶圆的结合,等离子体切割是结合阶段之前晶粒分离的更好的解决方案。

混合结合…以及为什么保持晶粒完整性很重要

混合结合是使用微小的铜焊盘连接(而不是传统的微凸块)在异质晶粒之间创建永久结合的工艺。 这种连接晶粒的方法可以提高高级 3D 设备堆叠中的互连密度和功能,提供比铜微凸块多 1,000 倍的输入输出连接,并将信号延迟驱动到接近零的水平。 混合结合可提高性能,而不会对功率和信号造成任何损失。 其他优势包括带宽扩展、内存密度更高以及功率更高和速度更快。

随着较小互连件的密度增加,表面清洁度对于实现可靠的晶粒到晶圆混合结合和优化良率变得至关重要。 表面的任何颗粒碎屑或激光损坏都可能导致晶粒表面无法正确接触晶圆并导致不完全粘合。 晶粒完整性对于承受粘合和堆叠的应力和应变也很重要。 如果有一个晶粒出现故障,这将导致整个芯片堆栈出现故障。

生产证明

大批量制造对工艺步骤的成功实施要求很高。 对于众多晶圆刻蚀应用而言,自动端点检测(EPD)至关重要,可确保精确控制工艺流程、保障一致性,从而稳定实现高成品率。 晶圆划片在薄膜框架载体中的胶带表面上进行,以便在切割完成后将晶粒固定到位。 在等离子切割工艺接近其终点时保护胶带对于完成晶粒分离而不会使胶带暴露在过热或等离子攻击下至关重要。 为实现这一目标,KLA Claritas和Sentinel工艺监测和控制系统对工艺和基面条件进行必要的监督。

根据晶粒尺寸,等离子切割的吞吐量可以超过所有其他方法的吞吐量,因为它是一种单程方法,晶圆只处

封装制造商继续通过全自动化优化其操作,通过架空轨道(OHT)或自动导引车(AGV)在工厂内移动晶圆。 KLA 支持这些增强的用于等离子切割的晶圆处理功能。 Mosaic OHT的设计旨在支持最多4个工艺模块,可混合运行薄膜框架载体(FFC)和晶圆,同时进行自动架空运输。

半导体创新要求高质量

等离子切割为锯切或激光切割等传统划片方法提供了行之有效的替代方案,也更符合业内创新型新技术的需要。

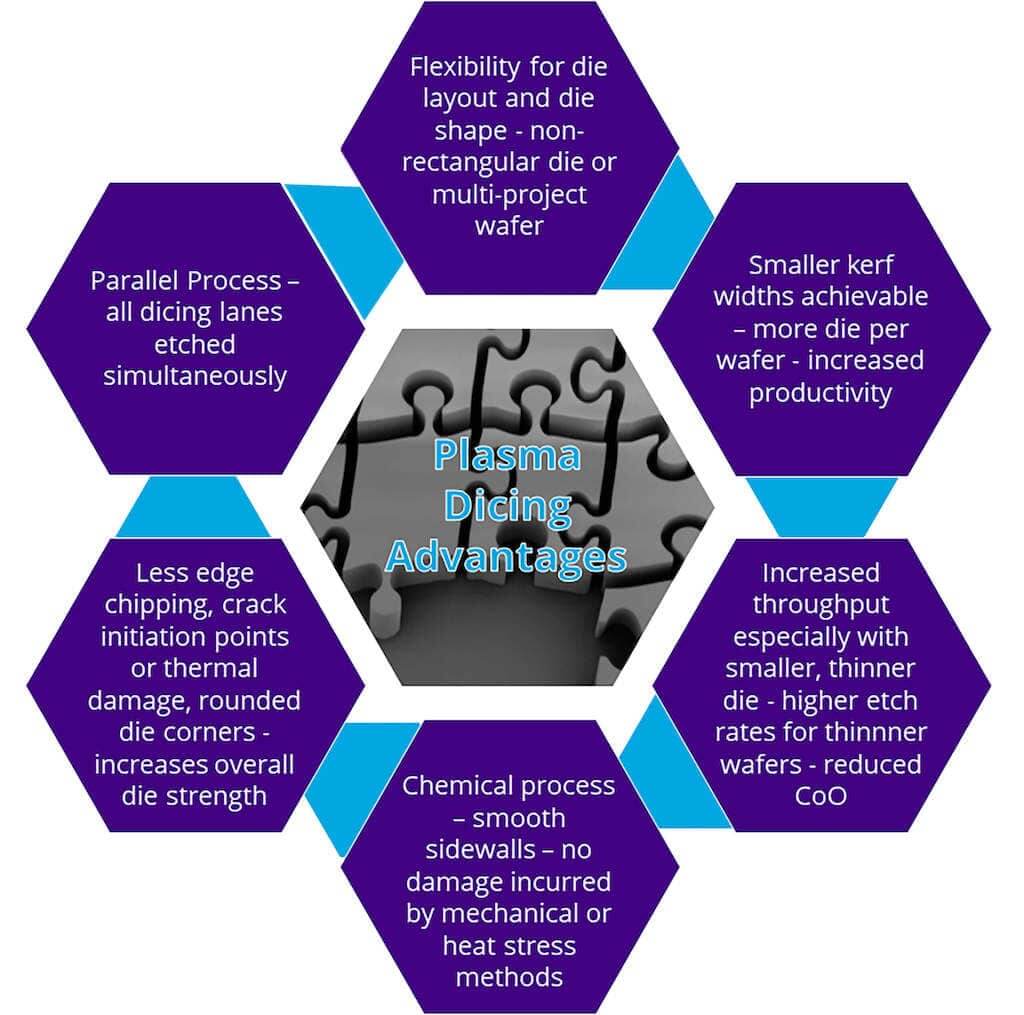

主要优势总结:

- 硅刻蚀速率快,可实现高晶圆/晶粒吞吐量

- 当晶粒与其他晶粒结合以进行复杂的多芯片封装时,更清洁的分离方法对于任何后续集成步骤至关重要

- 较小的切口宽度可释放宝贵的晶圆空间,这可用于每个晶圆更有活性的晶粒,这样可减少晶圆和前端设备的成本

- 通过避免与激光或锯切相关的损坏保持晶粒强度

- 自动端点检测(EPD)可确保工艺得到精细控制、保持一致性,实现高成品率生产

- 特定晶圆和框架处理平台应能将等离子切割从研发和原型制作应用推向大批量生产

如欲进一步了解有关等离子切割相对于传统方法的优势以及它们如何影响制造工艺,请向我们发送电子邮件。

关注我们